| 일 | 월 | 화 | 수 | 목 | 금 | 토 |

|---|---|---|---|---|---|---|

| 1 | 2 | 3 | ||||

| 4 | 5 | 6 | 7 | 8 | 9 | 10 |

| 11 | 12 | 13 | 14 | 15 | 16 | 17 |

| 18 | 19 | 20 | 21 | 22 | 23 | 24 |

| 25 | 26 | 27 | 28 | 29 | 30 | 31 |

- 오픽

- 영어회화

- C언어

- 영어공부

- 머신비전

- Vision

- 직장인

- machinevision

- 4차산업

- 동사

- 프로그래밍

- 초보영어

- 특수대학원

- ComputerVision

- 코딩

- 파이썬gui

- 영어기초

- 파이썬

- 3dprinter

- Ai

- 머신러닝

- 인공지능

- 산업대학원

- opencv

- 대학원

- 영어

- 석사

- 딥러닝

- Python

- coding

- Today

- Total

미래기술연구소

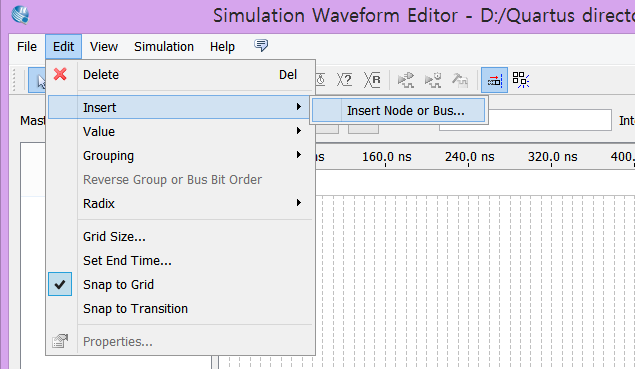

HDL Quartus II 13.1 (64-bit) Web Edition 본문

- 안녕하세요 이번 챕터에서는 지난번 임베디드 하드웨어 설계를 위한 기본 지식들을 정리해 둔 것에서 이제는 실제로 하드웨어 기술을 통한 회로 설계를 위해 Hardware Description Language (하드웨어 기술 언어) 중 하나인 Verilog 언어를 사용할 수 있는 개발환경 Quartus II 13.0 sp1을 소개해드리려고 합니다.

FPGA칩이 있는 보드만 있다면 Quartus 프로그램을 이용하여서 자신이 설계한 것을 직접 동작하는것 까지 확인하여 볼 수도 있답니다. (현재 Quartus는 쉽게 인터넷 검색을 통해서 Intel 사이트에서 다운로드 가능합니다.)

Intel® FPGAs and Programmable Devices - Intel® FPGA

FPGA or field programmable gate array is a semiconductor integrated circuit where electrical functionality is customized to accelerate key workloads.

www.intel.com

Quartus를 통해서 설계를 하면 장점으로는 컴파일 후 바로 설계된 회로도를 직접 볼 수 있다는 점과 시뮬레이터를 통해서 Timing Diagram을 확인 할 수 있다는 것입니다.

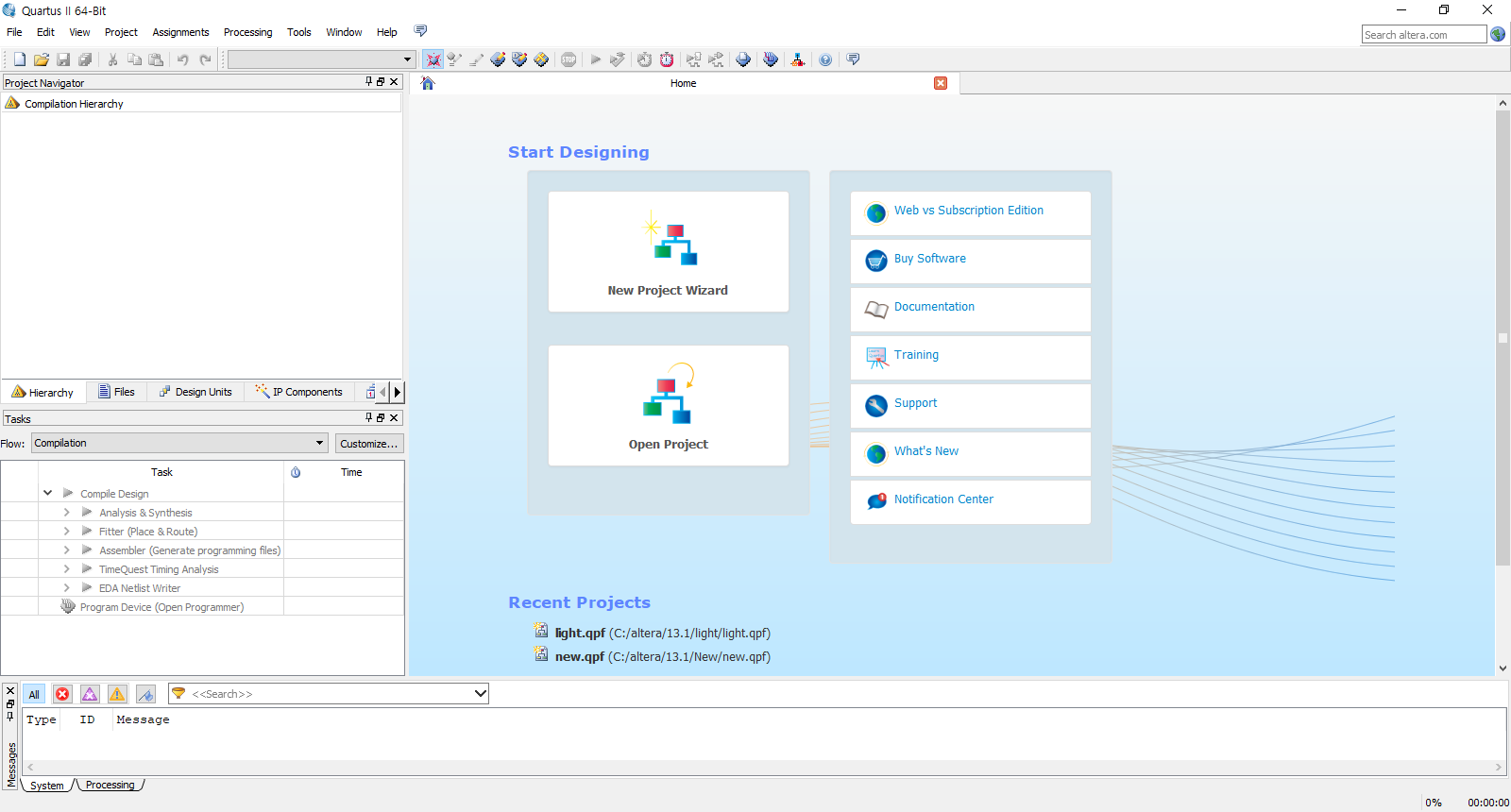

먼저, Quartus를 시작하면 다음과 같은 화면이 뜹니다.

*Quartus 첫 실행 화면

아마 첫 시작 화면은 다음과 같을 거구요. 최근 진행 했던 프로젝트가 있다면 저와 같이 바로 불러올 수 있는 디렉토리도 뜰 것 입니다.

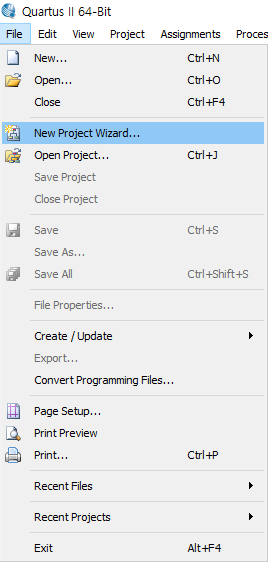

HDL에서도 기존 프로그래밍과 마찬가지로 프로젝트 생성을 가장 먼저 할 필요가 있는데요

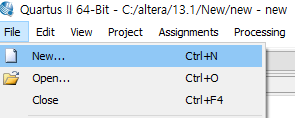

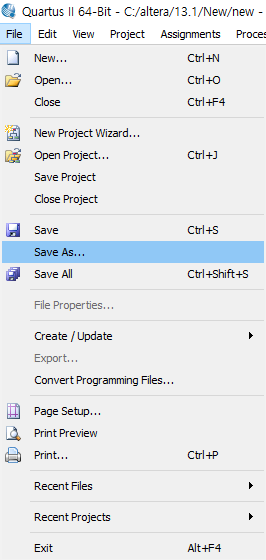

좌상단 File -> New Project Wizard 를 클릭하시면 다음과 같은 프로젝트 생성 창이 뜨게 됩니다.

*프로젝트 생성 창

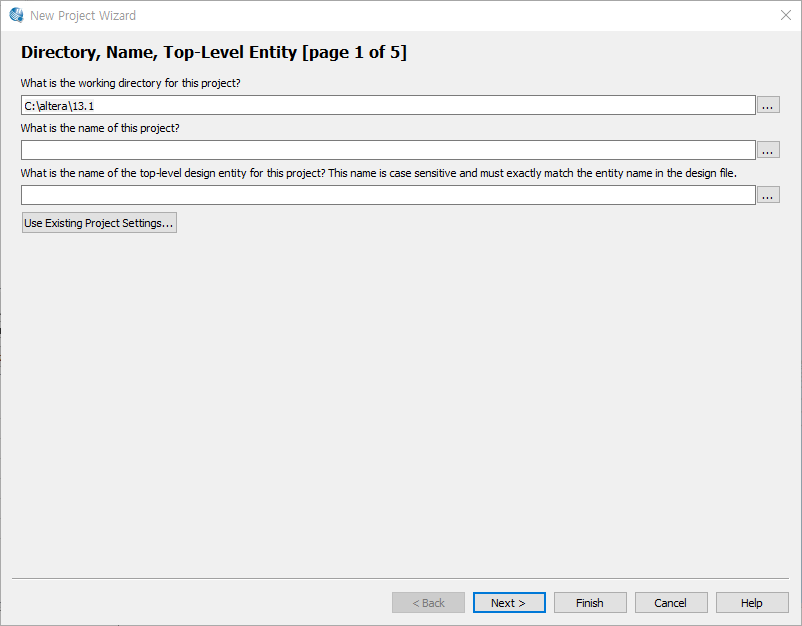

그럼 이제 자신이 프로젝트를 생성 할 디렉토리를 찾아 지정해주고 이때 지정할 디렉토리에 프로젝트 폴더를 하나 만들면 좋습니다. ('프로젝트 폴더명' = '프로젝트 명' 을 같게 하여 주시는 것이 좋습니다<추후 오류방지>)

*프로젝트 폴더 및 프로젝트 명

계속해서 Next 클릭 해주시고 자신이 가진 보드 명과 동일한 보드 명을 찾아서 Finish해주시면 프로젝트 생성이 완료 됩니다. 보드마다 컴파일 시 Logic Unit 구성과 갯수가 서로 다를 수 있기 때문에 보드를 통해서 직접 연결하여 작동을 확인하기 위해서는 보드 명이 정확히 일치해야 합니다. (가지고 계신 보드가 없다면 따로 찾지 않으셔도 시뮬레이션 하시는 것과는 무관합니다.)

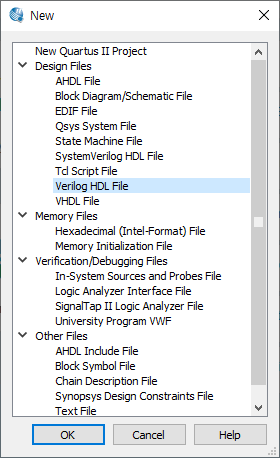

프로젝트 생성 후 코드를 작성할 .V 파일을 만들어 줄 건데요.

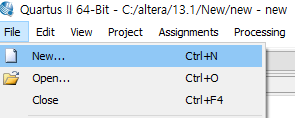

File -> New -> Verilog HDL File을 클릭해주시면 .V 파일이 생성됩니다.(veriloger 로 작성할 예정이기 때문)

파일 생성 후 아래와 같은 화면이 나타날 것입니다.

*v파일 생성 직 후

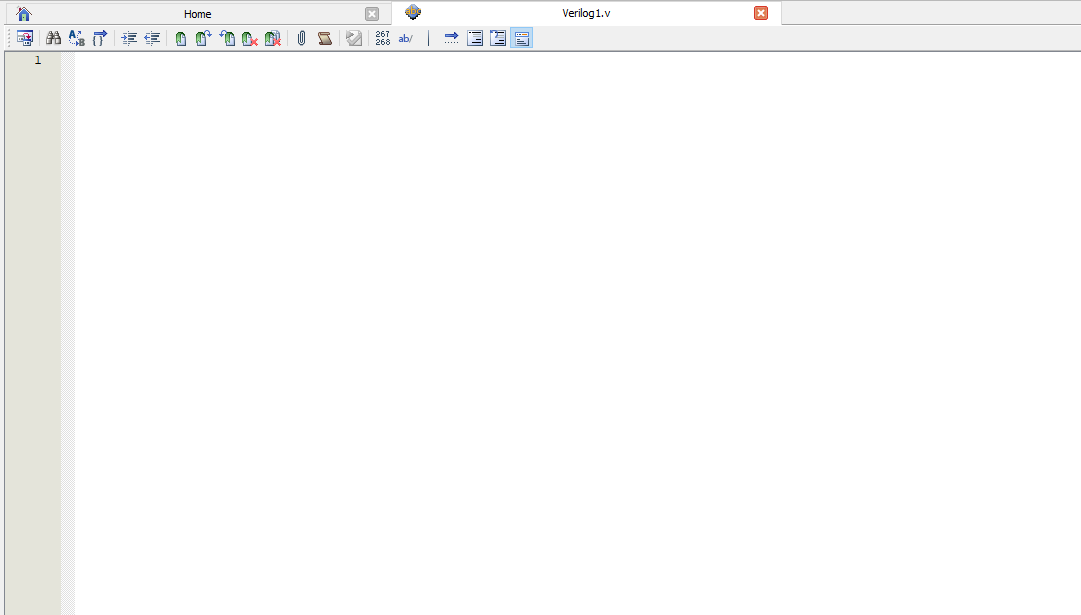

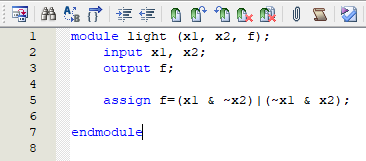

다음 순서는 아래와 같이 간단히 코드를 작성 하였다면 Ctrl+S(저장)를 눌러서 파일을 저장하는 것입니다.

*이때, Top Module의 module 이름이 'new'와 같이 생성한 프로젝트 명과 일치하여야 컴파일 오류가 발생하지 않습니다! 따라서 저는 위에서 프로젝트 명을 new로 하였으므로 module 명을 new로 통일시켜 주었습니다.*

module light (x1, x2, f);

input x1, x2;

output f;

assign f=(x1 & ~x2)|(~x1 & x2);

endmodule

*간단한 코드 작성

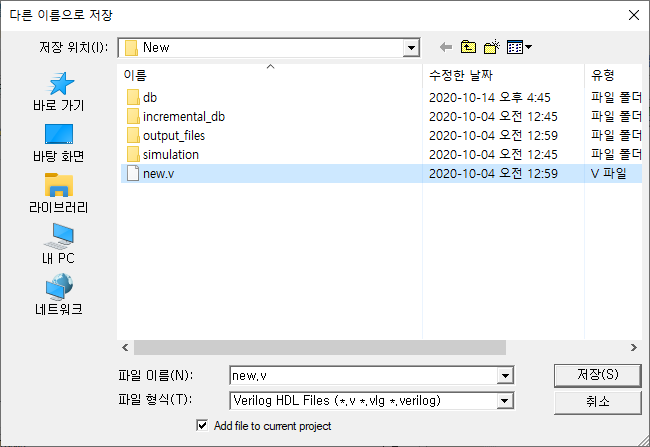

파일 저장 시에도 Top module 명과 같은 이름으로 파일이름.v 작성하여 저장하여주시면 됩니다!

*파일 저장

파일 저장이 완료 되었다면 작성한 코드를 통해서 컴파일도 해보고 시뮬레이션도 해보아야 할텐데요

다음과 같이 진행하시면 됩니다!

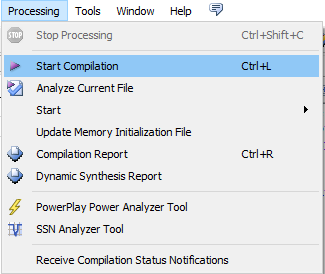

좌상단 Processing -> Start Compilation 을 누르거나 단축키(Ctrl + L)을 누르면 작성한 코드가 컴파일 되기 시작합니다.

*진행중인 컴파일 화면

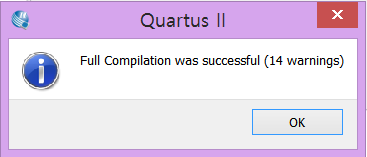

*컴파일 완료 알림

컴파일이 완료되면 위와 같은 알림 창이 표시 됩니다.

Warning이 뜨는 것은 제가 따로 보드에 넣을 Pin 번호 입력들을 안해주어서 뜨는 것이니 무시하셔도 무관합니다.

이제 시뮬레이션을 통해서 작성된 코드대로 하드웨어 컴파일러가 의도대로 잘 동작하는 회로를 만들어 주었는지 확인해 볼 필요성이 있기에 시뮬레이션 하는 방법은 다음과 같습니다.

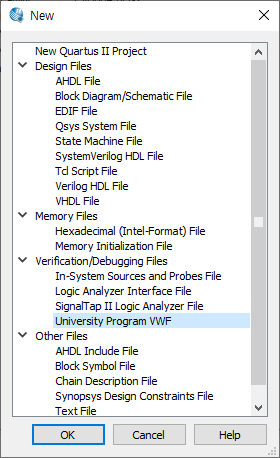

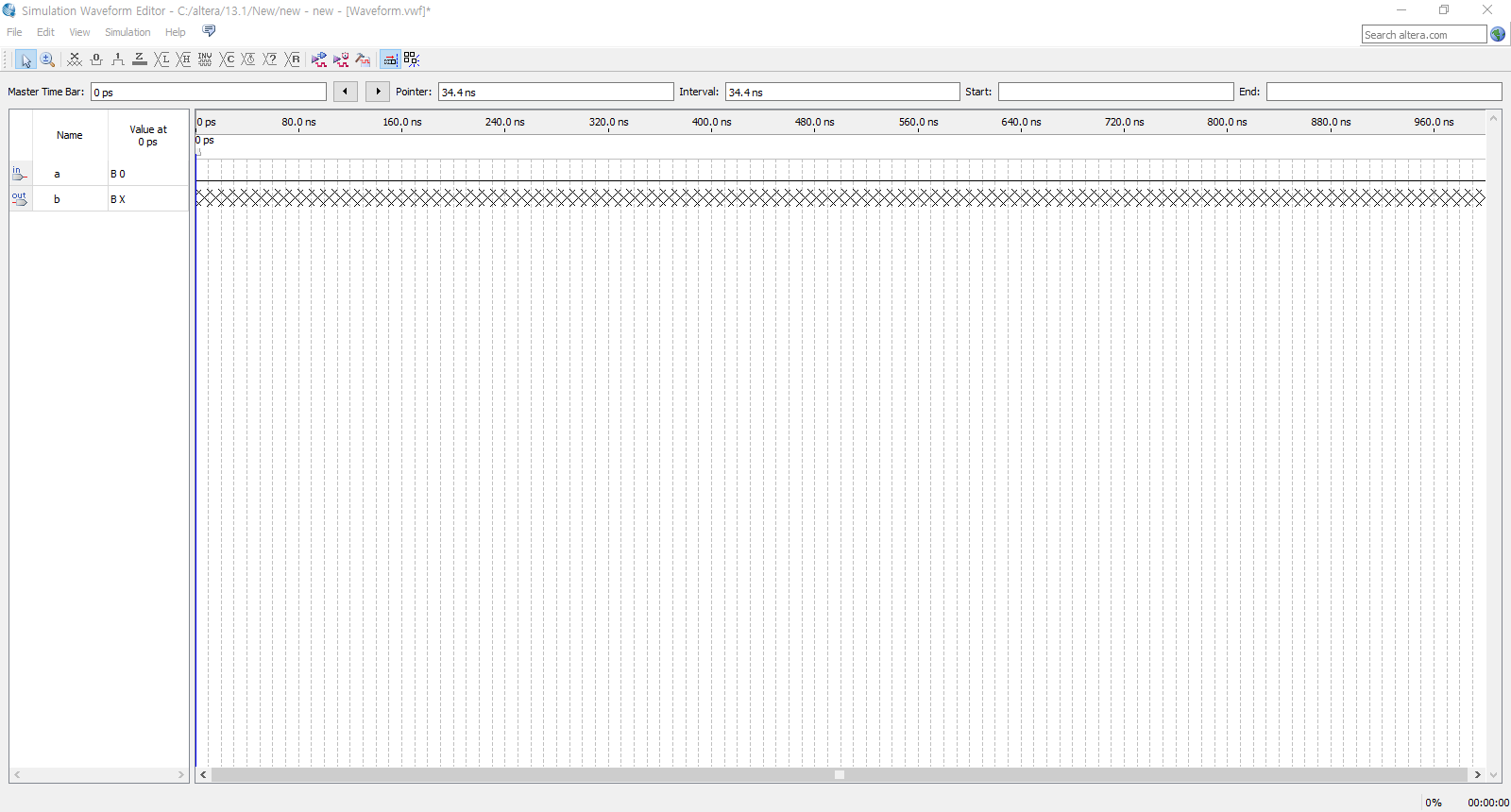

좌상단 File -> New -> University Program VWF를 클릭하여서 아래와 같은 Waveform 창을 띄웁니다.

*시뮬레이션 Timing Diagram 창

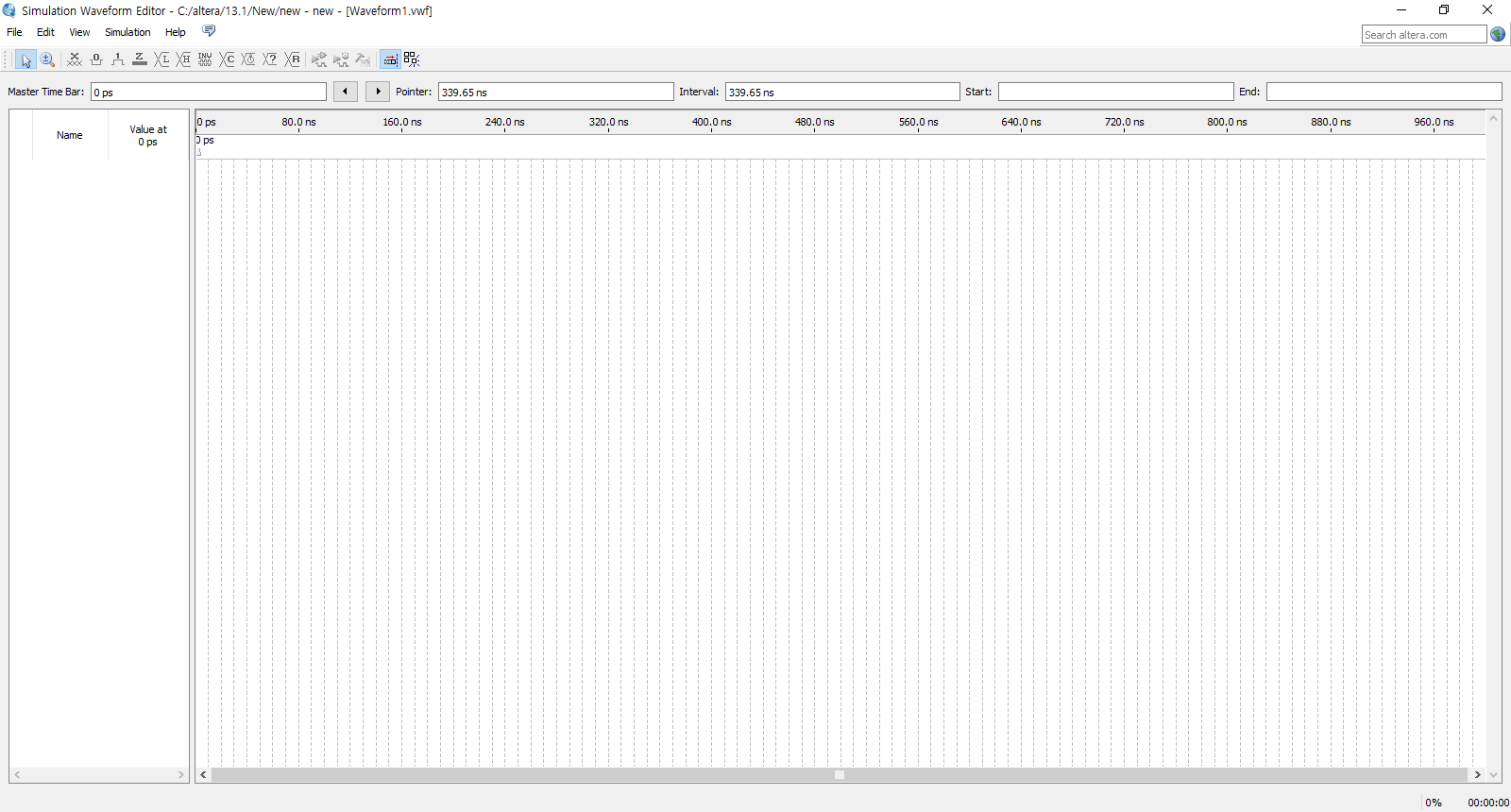

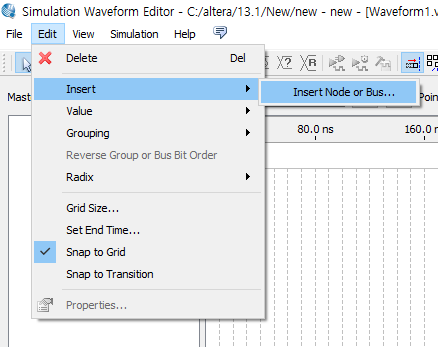

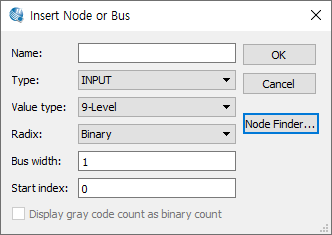

Edit -> Insert -> Insert Node or Bus 를 클릭 후 Node Finder를 클릭하시면 아래와 같이 Node Finder가 뜹니다.

*Edit -> Insert -> Insert Node or Bus

*Node Finder

*Node Finder

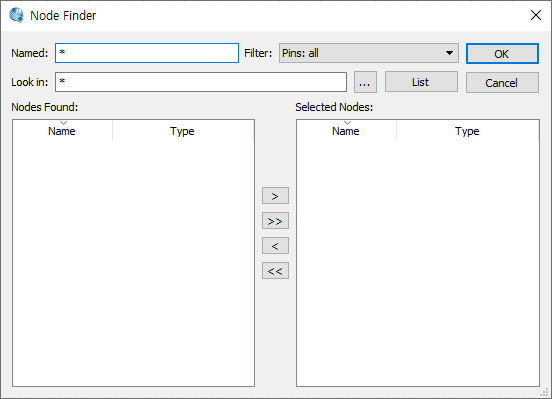

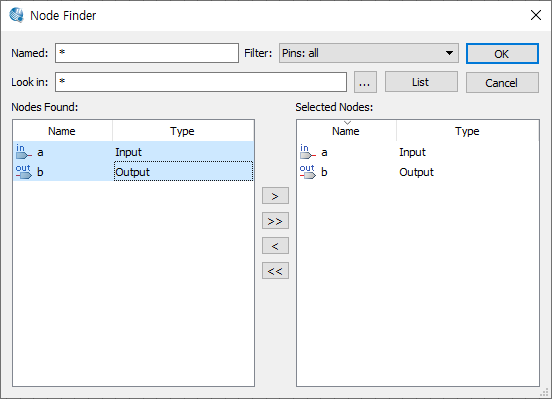

Filter를 통해서 원하는 레지스터 별 혹은 Input & Output을 골라서 시뮬레이터를 통해서 확인을 할 수 있습니다.

List 버튼을 누르고 >> 버튼을 통해 모든 Input & Output을 한번에 가져올 수 도 있습니다.

*a는 IN / b는 OUT

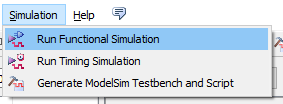

OK 버튼을 누른 뒤 자신이 원하는 INPUT 파형을 작성 한 뒤 Simulation -> Run Functional Simul / Run Timing Simul 을 통해서 시뮬레이션을 시작하시면 됩니다.

(Run Functional 은 Delay가 없이 나오는 파형이고 Run Timing은 Delay를 모두 고려해서 나오는 파형입니다.)

시뮬레이션 결과

*시뮬레이션 결과 창

위와 같이 시뮬레이션이 완료 되었고 제가 작성한 입력에 반전되는 조합회로를 작성 한 것처럼 의도대로 잘 시뮬레이션이 된 것을 확인할 수 있었습니다.

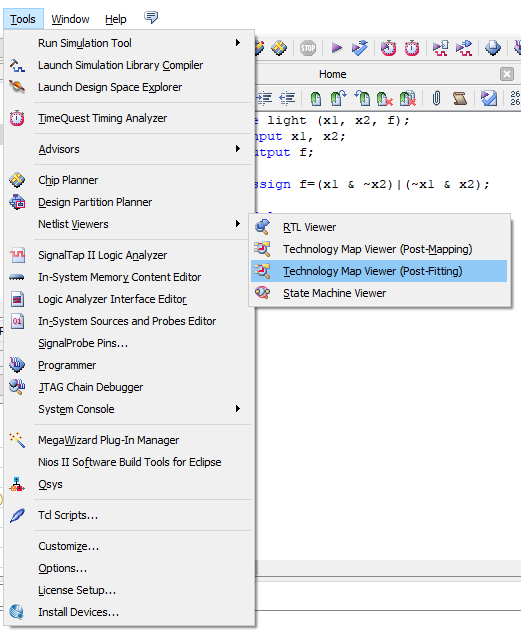

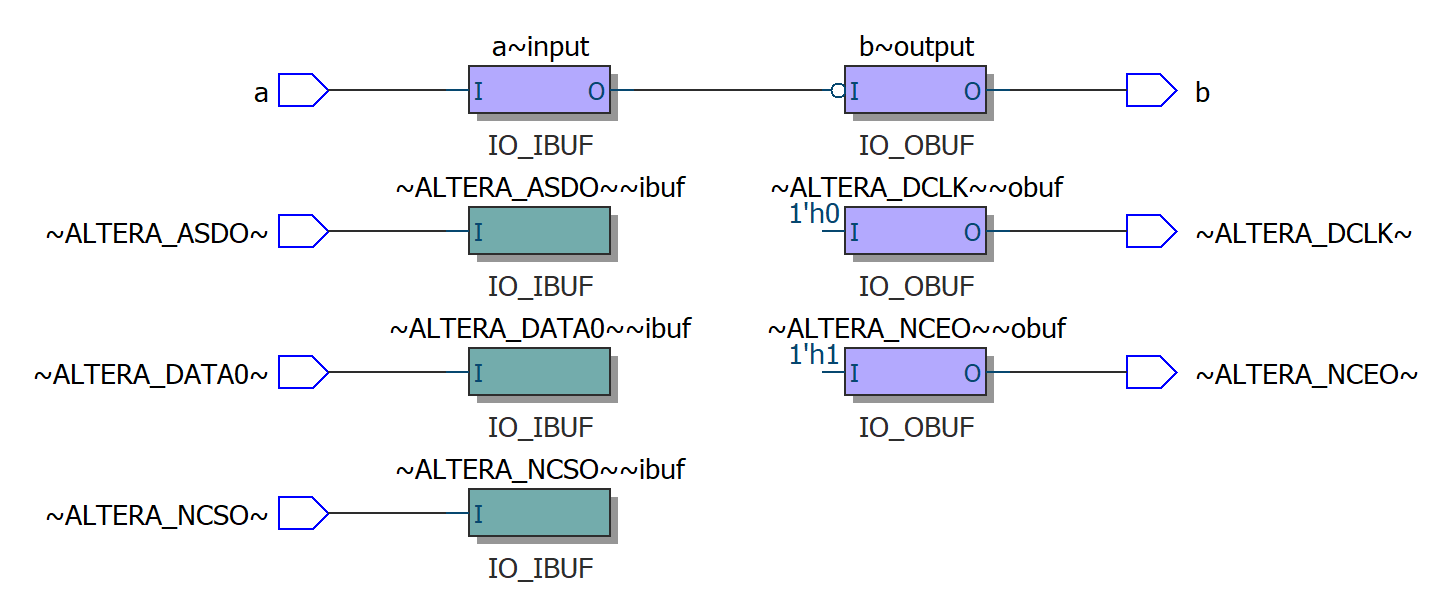

또한 상단 Tools -> Netlist Viewers -> Technology Map Viewer를 통해서 조합된 회로들의 형상을 볼 수 있습니다.

*Tools -> Netlist Viewers -> Technology Map Viewer

또한, Altera 보드에 직접 연결하여 확인해보고 싶으시다면 USB-Blaster를 설치하고 Pin Planner의 INPUT/OUTPUT Pin번호 설정을 한 뒤 Programmer를 통해서 진행 하실 수 있습니다.